On May 29th local time, another paper on chip materials led by Chinese scientists was published in Nature.

In the study, the Liaoning Material Laboratory, in collaboration with Shanxi University, the Institute of Metal Research of the Chinese Academy of Sciences, Sun Yat-sen University, the University of Chinese Academy of Sciences, Shandong University, and other institutions, jointly designed a quantum effect doping paradigm based on van der Waals interface intercalation, aiming to achieve simple, stable, and reliable p-type doping of two-dimensional semiconductors.

Through this, they obtained p-type transistors with high mobility, high on-state current, high on-off ratio, and low hysteresis, which has promoted the development of two-dimensional semiconductor electronic devices.

This simple doping method, which does not damage the channel material, regulates the carrier polarity of the two-dimensional semiconductor channel through van der Waals interface coupling.

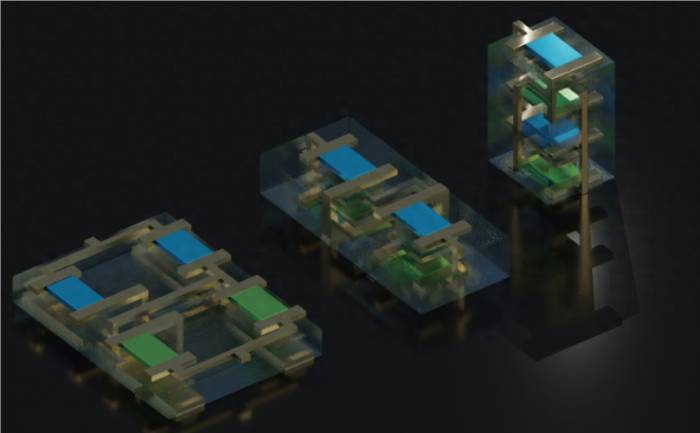

Using this regulation strategy, it is also possible to achieve two-dimensional material complementary logic circuits in the three-dimensional vertical direction. This method expands the established route of silicon-based logic circuits confined to the two-dimensional plane and provides ideas for the development of future two-dimensional semiconductor devices in the post-Moore era.The peer reviewers of the paper stated that by adopting a brand-new quantum effect doping route, the researchers in this study were able to produce band structure control and achieve a polarity transition from n-type to p-type in two-dimensional semiconductors simply by using interlayer insertion.

Advertisement

This two-dimensional semiconductor doping method is characterized by cleanliness, stability, and simplicity, and can be adapted to the manufacturing of three-dimensional vertical integrated circuits while maintaining the high carrier mobility advantage of two-dimensional semiconductor channel materials.

In addition, the team also demonstrated a variety of functional three-dimensional interconnected complementary logic circuits using this new doping method, with up to 14 layers of van der Waals two-dimensional materials in the vertical direction.

This kind of free design of vertical logic circuit configuration in a three-dimensional interconnected manner is one of the important demonstrations in the field of two-dimensional material electronic devices to date.

The room temperature hole mobility of the p-type field-effect transistors obtained through this new doping method is as high as 425 cm^2/(V·s), and the on-off ratio reaches 10 to the power of 6.It can remain stable in room temperature atmosphere for more than a year, which is a very significant advantage for the three-dimensional vertical integration of two-dimensional semiconductor complementary logic circuits.

In general, this achievement has broken through the dimensional limitations of two-dimensional planar transistor integration, providing new possibilities for further improving the integration density of transistors.

At present, the main bottleneck of this approach lies in the difficulty of obtaining a large-area growth of interface-controlled insulating layers.

If a large-area growth of CrOCl insulating layer can be achieved on this basis, it will be possible to further obtain uniform and controllable p-type two-dimensional semiconductor transistors, and even large-scale interlayer interconnected vertical complementary logic circuits.Starting from the Transistor Half a Century Ago

Currently, as the processing precision of silicon semiconductor technology further approaches the physical limits, the improvement of integrated circuit integration in the "post-Moore era" will mainly rely on innovative device architectures, optimization of process flows, and the development of disruptive new materials.

Over the past few decades, the development has been very rapid, from the planar transistor structures with a size of tens of micrometers in the 1970s, to the fin field-effect transistors in the 1990s, to the recent gate-all-around transistors and vertically stacked complementary field-effect transistors with completely new device architectures.

Among them, the vertically stacked complementary field-effect transistor structure's PMOS (n-type substrate, p-channel, a MOS tube that transports current by the flow of holes, positive channel Metal Oxide Semiconductor) and NMOS (N-type Metal-Oxide-Semiconductor, N-MOS) devices are stacked in the vertical space, controlled by a common gate located between the NMOS and PMOS.

From the earliest planar field-effect transistors, to fin field-effect transistors, and then to the most advanced gate-all-around transistors. The miniaturization of silicon semiconductors has always followed the strategy of in-plane integration.The vertical stacked complementary field-effect transistor (CFET) architecture is believed to reduce the area of integrated circuits by 42-50%, thus enabling higher integration density and reducing the cost by 12% compared to traditional planar Complementary Metal Oxide Semiconductor (CMOS) devices.

Therefore, it expands the possibility of further extending Moore's Law to the node below 1nm.

However, so far, the updates and iterations of silicon-based transistors have all been achieved by various means to reduce the "in-plane" size of the transistors and increase the transistor density.

There is a deep reason for the continuous miniaturization of silicon-based transistors in the in-plane "involution."

For the front-end process of silicon-based semiconductors, it usually relies on ion implantation on the surface of single-crystal silicon to obtain p or n-type doping.This doping process greatly limits the space for the vertical upward development of silicon-based semiconductor logic units.

Multi-layer stacked logic circuits can, in principle, alleviate the size crisis and extend Moore's Law.

From the perspective of basic research, the exploration of the three-dimensional vertical architecture logic circuit direction can provide references for various aspects such as thermal management, process technology, and material design of three-dimensional multi-layer interconnection circuits.

Two-dimensional semiconductors have a nanoscale thickness (typical molybdenum disulfide monolayer is only 0.6nm), which is naturally friendly to vertical multi-layer stacking, and theoretically can be vertically integrated infinitely.

Moreover, in recent years, breakthrough progress has been made in the large-area, high-quality, low-temperature growth preparation of two-dimensional semiconductors such as molybdenum disulfide.The advancements in these technologies have significantly enhanced the application potential of two-dimensional semiconductors, making them an increasingly important alternative material system for future semiconductors.

Therefore, both the industry and academia are actively conducting research on the integration technology of two-dimensional semiconductors.

Currently, the key directions of three-dimensional integration research for two-dimensional semiconductors can be summarized into two categories:

Firstly, the improvement of material properties, including obtaining two-dimensional semiconductor materials with higher mobility and better contact, higher uniformity, and better p-type doping materials.

Secondly, the optimization of vertical integration processes, including hybrid-dimensional integration and multi-layer transfer integration.The project lasted nearly three years, with dozens of people involved in the research and development.

This study chose a different approach. The team's preliminary research indicated that interfacial coupling based on quantum effects might regulate the band structure of two-dimensional electron gas and induce brand-new physical phenomena.

The researchers stated that the original intention of the project was to achieve interfacial coupling between few-layer transition metal dichalcogenide semiconductor materials and two-dimensional antiferromagnetic insulator CrOCl, expecting to observe some interesting physical phenomena at low temperatures.

At the beginning of the project, they encountered a major setback.In order to reduce the scattering of carriers within the channel by the substrate, the research group utilized the two-dimensional layered insulating material boron nitride to encapsulate transition metal dichalcogenides/CrOCl.

By employing reactive ion etching technology, the top layer of boron nitride was etched to fabricate electrodes.

Tests revealed that the batches of devices prepared were non-conductive, which is a common occurrence in scientific exploration as experimental failure is a norm.

Subsequently, they reviewed the entire process and redesigned the control experiments, abandoning the use of boron nitride encapsulation to minimize the impact of etching and other processes, thereby better focusing on the performance regulation of CrOCl on transition metal dichalcogenides.

By the end of 2021, after continuous optimization of the process, they observed the hole doping effect of CrOCl on transition metal dichalcogenides in this composite system of transition metal dichalcogenides/CrOCl.Previously, n-type field-effect transistors based on two-dimensional semiconductors have made significant progress in performance enhancement, even rivaling the performance of silicon-based n-type transistors.

However, the performance improvement of two-dimensional p-type transistors has been relatively slow. Therefore, they are now going to focus on improving the device fabrication process, enhancing the performance of transition metal dichalcogenide/CrOClp-type transistors, and designing comparative experiments to deeply study the doping mechanism.

In the first half of 2022, they characterized the impact of the thickness of two-dimensional transition metal dichalcogenide semiconductor MoS2, the thickness of two-dimensional layered insulator CrOCl, and the contact electrode material of the transition metal dichalcogenide on device performance.

Based on the above exploration, the team has preliminarily optimized key parameters such as the selection of material thickness for hole doping, the choice of contact electrodes, and the fabrication process conditions, and has achieved superior electrical performance of p-type field-effect transistors, with both carrier mobility and on-off ratio reaching high levels.

At the same time, they have gained a preliminary understanding of the doping principle. The team's theoretical collaborators believe that this doping mechanism is related to the synergistic effect of interfacial charge transfer and long-range electron-electron interactions at the interface between CrOCl and transition metal dichalcogenide semiconductors.Based on this, the team began to explore the use of this doping method to construct CMOS logic circuits.

In the second half of 2022, they combined the transition metal dichalcogenide /CrOClp field-effect transistors with the intrinsic transition metal dichalcogenide n-type field-effect transistors for in-plane circuit interconnection to form a "NOT" gate logic device, preliminarily verifying the feasibility of using this doping method for the construction of CMOS logic circuits.

Furthermore, to fully utilize the unique vertical stacking compatibility of this doping method and to improve circuit integration, they vertically stacked the p-type field-effect transistors with the n-type field-effect transistors.

That is, controlled by the same gate electrode, they achieved a vertical stacked complementary field-effect transistor configuration of a vertical inverter.

Subsequently, the research group verified the prototype of a three-dimensional vertically integrated logic device based on two-dimensional semiconductors.By stacking four n, p transistors in the vertical direction and interconnecting the circuits, they successfully achieved a full three-dimensional "AND-NOT" gate logic gate (3D NAND) with a 14-layer van der Waals vertical stacking of two-dimensional materials.

Subsequently, they discussed issues such as thermal management and data access delay through simulation, which is of significant reference value for the development of three-dimensional integrated circuits.

In addition, the team also further improved the contact through methods such as annealing and electrode engineering, and made a three-dimensional integrated vertical static random access memory device (3D SRAM).

Purchased experimental equipment from Taobao, and the paper was finally published in Nature.In fact, when the project reached its mid-term, they encountered a bottleneck in understanding the mechanism.

After a period of experimentation, the performance of the transistors built based on this new type of p-type doping method has reached a stable and excellent level, but the underlying physical mechanism is temporarily difficult to reach a self-consistent conclusion.

The first author of the paper, Guo Yimeng, said: "After consulting with my teachers and experts in the field of theory, several possibilities were obtained."

Professor Wei Suhuai from the Beijing Computational Science Research Center believes that this may be a doping effect caused by a defect, or a Mott process, and of course, more complex electron correlation effects are not ruled out.

In order to rule out the effect dominated by defects, the research team conducted a large number of control experiments. The results showed that once the cleanliness of the molybdenum disulfide and chromium oxychloride interface was compromised, the p-type doping effect would disappear, accompanied by a large hysteresis, thus the defect image could not be self-consistent.The exclusion of the Mott process, however, requires a theoretical demonstration that the electron doping concentration is insufficient to trigger this process.

Professor Liu Jianpeng's research group at ShanghaiTech University systematically explained the important role played by interfacial quantum effects from a model perspective, combined with the experimental charge transfer concentration, which essentially excludes the Mott picture.

Ultimately, the team believes that this clean, stable, and simple two-dimensional transition metal dichalcogenide semiconductor van der Waals intercalation polarity control effect comes from a very subtle and should be a universal effect for multiple materials.

Therefore, this new principle semiconductor based on quantum effects has expanded new ideas for the design and control of two-dimensional semiconductor materials and device structures.

There is also an event that left the deepest impression on Guo Yimeng when he first measured the storage behavior of the 3D SRAM device.The process of vertically 3D assembling four transistors and testing their functionality involves a series of sample preparation and measurement procedures, which was completely new to Guo Yimeng, who is still a student.

The manufacturing of 3D logic circuits is of great significance to the integrity and innovation of this work.

To intuitively grasp this knowledge, Teacher Wang Hanwen from the research team bought commercially available p- and n-MOS transistors with suitable performance from Taobao, soldered them onto the PCB circuit board according to the SRAM circuit, and learned the SRAM testing operation based on this.

Indeed, after a few attempts, they quickly measured the storage behavior of the SRAM.

"Although this small detail is insignificant in the entire experimental process, this kind of learning process that combines education with entertainment has greatly boosted my confidence in subsequent experimental work," said Guo Yimeng.Later, they successfully achieved the storage behavior of 3D SRAM circuits prepared by controlling the polarity of two-dimensional semiconductors.

Eventually, the related paper was published in Nature [1] under the title "Van der Waals polarity-engineered 3D integration of 2D complementary logic."

Guo Yimeng and Li Jiangxu from the Institute of Metal Research of the Chinese Academy of Sciences, Zhan Xuepeng from Shandong University, Wang Chunwen from the University of Chinese Academy of Sciences, and Li Min from ShanghaiTech University are the co-first authors of the paper.

Researcher Li Xiuyan from the Institute of Metal Research of the Chinese Academy of Sciences, Professor Hou Yanglong from Sun Yat-sen University, Professor Zhou Wu from the University of Chinese Academy of Sciences, Associate Researcher Wang Hanwen from Liaoning Material Laboratory, and Professor Han Zhen from Shanxi University are the co-corresponding authors of the paper.

It is reported that the researchers' subsequent plans mainly focus on two aspects:Firstly, from the perspective of fundamental physics, the optoelectronic properties of PN junctions are studied.

Intrinsic n-type field-effect transistors and p-type field-effect transistors obtained after doping can not only serve as discrete NMOS units and PMOS units of CMOS logic circuits in the vertical direction, but also work as PN junctions to construct new types of optoelectronic sensors and detectors.

Secondly, from the perspective of cutting-edge applications, the p-type doping of the interfacial coupling effect of transition metal dichalcogenides/COC is used for the growth of large-area transition metal dichalcogenides/COC, and further for large-area three-dimensional integration.

To apply the hole doping technology suitable for three-dimensional integration to the current silicon-based integrated circuits, the first issue to be solved is the large-area growth of two-dimensional semiconductor materials and their corresponding CrOCl insulating layers.

However, despite the widespread attention to the research of two-dimensional semiconductors worldwide over the past decade, its development is still in a very early stage. The current literature reports, including this study, are all relatively preliminary explorations.The real application of two-dimensional semiconductors still faces a series of arduous challenges, such as how to increase the operating frequency, how to improve stability and uniformity, and how to resolve the heat dissipation and crosstalk issues between layers. Therefore, there are more problems waiting for researchers to work hard to overcome.