Recently, Dr. He Zhao from the King Abdullah University of Science and Technology in Saudi Arabia and his team have developed a neuromorphic memory device based on a quantum chip, supporting trillions of nodes per square centimeter.

Compared to previous similar systems, the scale of this system's network is 2-7 orders of magnitude larger. For each network node, it is composed of nanocircuits induced by quantum nucleation on thin films.

And this thin film is made of phase change material, which allows a single readout channel to consume only 0.07 nanowatts of electrical power.

Compared to the best artificial memory devices before, it has reduced the electrical power by 6 orders of magnitude and is 1 order of magnitude more efficient than the biological neurons in the human brain.

Due to the large number of neural network nodes in this chip and its excellent power efficiency, the research team has combined its quantum characteristics to create a new form of hardware security primitive.Security primitives are physical systems or devices that can generate unique and unreplicable digital fingerprints based on one-way physical phenomena.

Advertisement

The powerful capabilities of security primitives have attracted academic interest in the study of authentication systems. Current authentication methods such as passwords and biometrics have been proven to be vulnerable to hacking attacks and are no longer sufficient to protect users.

This research demonstrates that a new technology can be created through neural chips, which is protected by the laws of quantum mechanics and therefore not affected by hardware cloning.

The aforementioned new technology is immune to any type of artificial intelligence attack, both current and undisclosed.

Experimental results show that it has a reliability of 99.6%, a user authentication accuracy of 100%, and an ideal key uniqueness of 50%.The quantum properties it possesses are more than three times superior to the current best technology, while being able to store more than 21,104 keys within an area of only one square centimeter.

In terms of application prospects:

Firstly, it can achieve secure applications.

This chip can help ensure that critical infrastructures such as smart energy networks reject unauthorized access, contributing to the realization of smart cities with deep technological penetration.

In the future, if the technology reaches a more mature stage and the prototype based on this chip can be verified, it is expected that this technology can significantly curb cybercrime activities targeting private companies and government agencies.Secondly, it can be used for natural language processing tasks.

For example, it can perform language modeling, sentiment analysis, text classification, machine translation, and speech recognition, among others.

Due to the recurrent nature of the memory, it is particularly well-suited for processing sequential data such as text. At the same time, it also has the ability to capture complex patterns, which allows it to model the subtleties of language.

The large-scale neural network nodes based on on-chip neural memory and high power efficiency enable it to carry out real-time language processing applications in resource-constrained environments.Simulate opponents, verify attacks

In the study, the research team chose to use the phase change material Ge2Sb2Te5. The reason is that the phase change of the Ge2Sb2Te5 material can be induced and controlled by various means such as electric field, heat, and light.

Additionally, Ge2Sb2Te5 has a relatively fast phase change speed and the characteristic of non-volatile phase change process, making it more suitable for the development of this project.

When manufacturing the chip, to eliminate the impact of uneven substrates, they used a single-sided polished silicon wafer as the original substrate.

Then, a thin layer of silicon dioxide was deposited on the silicon wafer to serve as the final supporting substrate, thereby eliminating the impact of silicon as a semiconductor on the electrical signal test.Subsequently, it is necessary to deposit germanium-antimony-tellurium thin films. For this step, there are no reference operation parameters available.

Therefore, they need to summarize the parameters in advance, especially the thickness and time, and then select the appropriate deposition time to achieve the desired thickness.

In the process of electrode preparation, it is necessary to connect the circuit between any different electrode points based on the current-voltage detection of the chip.

This also means that the electrodes themselves must be isolated and not connected. To this end, the research team prepared a photomask, which, with the help of photolithography technology, exposes the positions for electrode deposition.

Gold has good conductivity, so the team chose it as the electrode material.Before depositing the gold film, they first deposited a thin layer of titanium film. The advantage of titanium film deposition is that it helps to reduce the delamination or detachment of the gold film during use due to temperature changes, stress, and other factors.

Then, they deposited thin gold films with thicknesses of 80 nanometers and 120 nanometers. However, even with the titanium film as an intermediate layer, the gold film still experienced delamination during the development process of the photoresist, so they reworked and prepared thicker gold films.

The wire bonding process on the chip involves using a wire bonding machine to connect the chip electrodes to the circuit board with micrometer-sized gold wires.

However, factors such as welding parameters, temperature control, pressure control, welding speed, atmosphere control, and gold film thickness can all affect the wire bonding process.

To this end, after several months of exploration, they finally determined the appropriate equipment parameters.In the stage of performance characterization, the research team used high-resolution transmission electron microscopy to characterize the microstructure of the germanium-antimony-tellurium (GST) thin film.

At the microscopic level, the GST thin film mainly consists of an amorphous structure and a small number of crystalline regions with diameters ranging from 5 to 7 nanometers.

In the study, the crystallographic data from the Bragg pattern indicated that the GST material has a polycrystalline nature.

At the same time, they used a conductive probe atomic force microscopy (AFM) device to test the electrical properties of the device at the nanoscale.

The results showed that in the test image, the coherent area of each point was a single pixel of 8 nanometers by 8 nanometers.By analyzing the changes in voltage and resistance, the research team found that when the voltage increases, the resistance will decrease by 1-4 orders of magnitude.

This not only follows the power law behavior, but also the micro-evolution will show continuous changes, and the material also shows a transition from amorphous to crystalline state.

With the help of in-situ high-resolution transmission electron microscopy, they tracked the situation of the germanium-antimony-tellurium thin film during the heating process.

The results showed that the growth of existing crystals and the growth of new quantum-sized crystals under thermal stimulation led to changes within the germanium-antimony-tellurium thin film.

For this reason, with the help of a probe station, they carried out current-voltage testing for quantum chips.Through this, they observed that the parameters of amorphous germanium-antimony-tellurium thin films began to exhibit reproducible and continuously tunable characteristics.

The quantum-scale nuclear fusion from amorphous thin films would generate nanocircuits. The next step is to develop a theoretical model to support such a hypothesis: a physical reservoir capable of supporting communication of nanocircuits originating from quantum-scale nucleation in amorphous thin films. Thus, they decided to utilize this characteristic to develop foundational security equipment and invest resources in researching this application.

Based on this, the team successfully developed an authentication system, which includes two parts: secure key generation and secure key authentication. The key generation follows the "challenge-response" model.

In terms of chip input, they provide a binary challenge string. In terms of chip output, they use a deep neural network to convert the response signal into a binary key string.

Subsequently, the research group designed a verification network. In designing the verification network, it is not only necessary to ensure that the authentication server only retains the challenge string, but also to ensure that no part can store a one-time key.Based on this verification network, they carried out key authentication and modeled a "rival" by simulating the system.

This "rival" is not only very familiar with the characteristics of the system but can also replicate all classical components except for the neural storage.

Based on this "rival," they assessed the system's resistance to statistical reasoning. The results show that attackers are unable to predict the relevant authentication instances.

Mentor: "You may have discovered something more important."It is also reported that when preparing the aforementioned quantum chip, the research team indicated that there was an element of luck involved.

This study was originally intended to focus on display applications and develop a new type of optical phase change material.

However, during the deposition process, they found through transmission electron microscopy that the conditions initially used in the deposition apparatus did not yield a uniform thin film, but instead resulted in an amorphous system composed of randomly aggregated grains.

As a result, when they obtained the first batch of samples, everyone was extremely disappointed, as none of the samples met the expected results.

After several attempts, they were almost ready to give up on the project. However, when they showed these initial results to their mentor, the mentor told them, "You may have discovered something more important."Thus, the team conducted an electronic measurement, and although they encountered exceptionally complex physical phenomena, the preliminary results looked promising.

After about another year, with the aid of high-resolution transmission electron microscopy, atomic force microscopy, Raman spectroscopy, and other methods, they conducted multiple investigations at the atomic scale and finally understood the working mechanism of the system, and created the aforementioned secure authentication system.

Recently, the related paper was published on arXiv[1] with the title "Quantum-activated neural reservoirs on-chip open up large hardware security models for resilient authentication."

Postdoctoral researcher He Zhao and doctoral student Maxim Elizarov are the co-first authors of the team, and researcher Li Ning is a co-author.

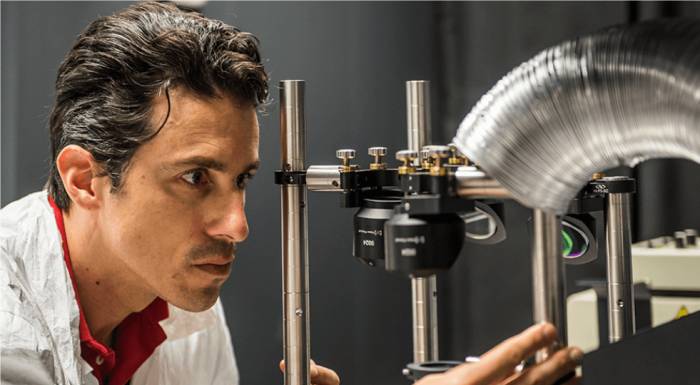

Professor Andrea Fratalocchi from King Abdullah University of Science and Technology in Saudi Arabia is the corresponding author.Figure | Andrea Fratalocchi (source: reference image)

Subsequently, the research team plans to develop an integrated solution for a neural chip. In the current scheme, the chip's operation is controlled by a probe station, which limits the ability to modulate the system response speed within milliseconds.

It is expected that after the improvement, real-time information processing will be possible, thereby enhancing the operational speed and power efficiency of the device.